Expertise

Computer-aided design for VLSI circuits, design for testability, hardware/software co-synthesis, low power and reliable computing

Areas of Specialization

Research Clusters

-

Professor

Electrical & Computer Engineering

-

Associate Member

Computing and Software

Overview

My general research interests lie in the broad area of methods and algorithms for the design of digital integrated circuits and systems. I have contributed to the fields of manufacturing test and post-silicon validation and debug. My recent interests have been expanded to embedded, low-energy and custom hardware-accelerated computing systems.

Did you know?

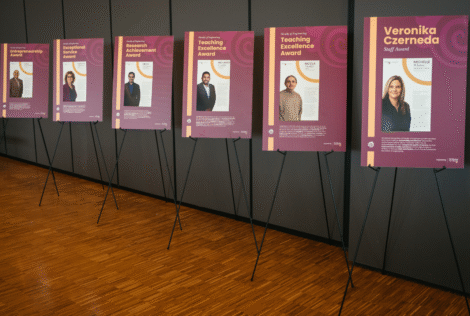

Dr. Nicolici won the Distinguished Engineering Educator from McMaster University in 2014 and the MSU Teaching Award from McMaster University in 2010.

Nicola Nicolici received the Dipl.Ing. degree in Computer Engineering from the “Politehnica” University of Timisoara, Romania, in 1997 and the Ph.D. degree in Electronics and Computer Science from the University of Southampton, U.K., in 2000. His research interests are in the area of computer-aided design and test for integrated circuits and systems. He has authored over 120 papers in this area.

Dipl. Ing. (“Politehnica” University of Timisoara, Romania) ; Ph.D. (Southampton University, U.K.)

- P.Eng.

- Distinguished Engineering Educator

- Dean’s Teaching Honour Roll for 2 courses – CompEng 3DQ5 and CompEng 4DS4

- Awarded an NSERC Discovery Accelerator Supplement (this prestigious award is in recognition of his outstanding research program in “post-silicon” validation methods for VLSI systems)

- Senior Member IEEE

Selected

P.T. Gonciari, B.M. Al-Hashimi, and N. Nicolici (2003)

Variable-Length Input Huffman Coding for System-on-a-Chip Test

IEEE TRANSACTIONS ON CAD, VOL. 22, PAGES 783-796

P.M. Rosinger, B.M. Al-Hashimi, and N. Nicolici (2004)

Scan Architecture With Mutually Exclusive Scan Segment Activation for Shift and Capture Power Reduction

IEEE TRANSACTIONS ON CAD, VOL. 23, PAGES1142-1153

H.F. Ko and N. Nicolici (2009)

Algorithms for State Restoration and Trace Signals Selection for Data Acquisition in Silicon Debug

IEEE TRANSACTIONS ON CAD, VOL. 28, PAGES 285-297

A.B. Kinsman and N. Nicolici (2010)

Bit-Width Allocation for Hardware Accelerators for Scientific Computing Using SAT-Modulo Theory.

IEEE TRANSACTIONS ON CAD, VOL. 29, PAGES 405-413, MARCH 2010

E. Anis Daoud and N. Nicolici (2011)

On Using Lossy Compression for Repeatable Experiments During Silicon Debug

IEEE TRANSACTIONS ON COMPUTERS, VOL. 60, PAGES 937-950

Z. Lak and N. Nicolici (2012)

On Using On-Chip Clock Tuning Elements to Address Delay Degradation Due to Circuit Aging

IEEE TRANSACTIONS ON CAD, VOL. 31, PAGES 1845-1856

Recent

P. Taatizadeh and N. Nicolici, “Emulation Infrastructure for the Evaluation of Hardware Assertions for Post-Silicon Validation,” IEEE Transactions on VLSI, vol. 25, pages 1866-1880, June 2017

X. Shi and N. Nicolici, “Generating Cyclic-Random Sequences in a Constrained Space for In- System Validation,” IEEE Transactions on Computers, vol. 65, pages 3676-3686, December 2016

View publications on Google Scholar.